最近做stm32项目,纠结过其启动方式。

看到篇不错的文章,转载一下。原文格式不太好,内容也有很多奇怪的地方(尤其是第二篇,就先认为原文是原创,只是作者的思路我不懂吧),都一一删改。想看原文的朋友链接如下:

http://www.ithao123.cn/content-3065243.html Duanxx的STM32学习: 启动模式,BOOT0和BOOT1详解

http://bluefish.blog.51cto.com/214870/1239098 上拉电阻与下拉电阻的作用

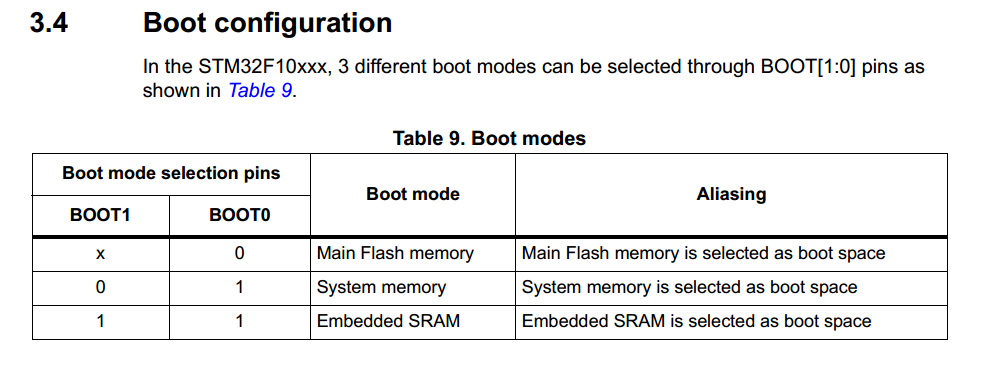

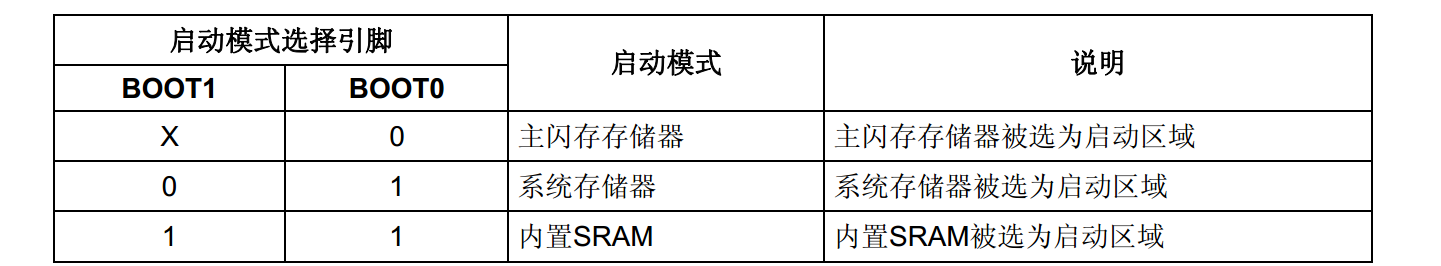

所谓启动,一般来说就是指我们下好程序后,重启芯片时,SYSCLK的第4个上升沿,BOOT引脚的值将被锁存。用户可以通过设置BOOT1和BOOT0引脚的状态,来选择在复位后的启动模式。

Main Flash memory是STM32内置的Flash,一般我们使用JTAG或者SWD模式下载程序时,就是下载到这个里面,重启后也直接从这启动程序。

System memory从系统存储器启动,这种模式启动的程序功能是由厂家设置的。一般来说,这种启动方式用的比较少。系统存储器是芯片内部一块特定的区域,STM32在出厂时,由ST在这个区域内部预置了一段BootLoader,也就是我们常说的ISP程序,这是一块ROM,出厂后无法修改。

一般来说,我们选用这种启动模式时,是为了从串口下载程序,因为在厂家提供的BootLoader中,提供了串口下载程序的固件,可以通过这个BootLoader将程序下载到系统的Flash中。但是这个下载方式需要以下步骤:

Step1:将BOOT0设置为1,BOOT1设置为0,然后按下复位键,这样才能从系统存储器启动BootLoader

Step2:最后在BootLoader的帮助下,通过串口下载程序到Flash中

Step3:程序下载完成后,又有需要将BOOT0设置为GND,手动复位,这样,STM32才可以从Flash中启动

可以看到,利用串口下载程序还是比较的麻烦,需要跳帽跳来跳去的,非常的不注重用户体验。

Embedded SRAM 内置SRAM,既然是SRAM,自然也就没有程序存储的能力了,这个模式一般用于程序调试。

假如我只修改了代码中一个小小的地方,然后就需要重新擦除整个Flash,比较的费时,可以考虑从这个模式启动代码(也就是STM32的内存中),用于快速的程序调试,等程序调试完成后,在将程序下载到SRAM中。

因此,比较常见的选择方式是BOOT0接地,当然啦,如果自己画stm32系统板的话,最好也要留下其他两个启动方式。对于大型程序使用SRAM进行调试还是很有必要的。

下面讲一下上拉电阻与下拉电阻的区别:

上拉电阻就是把不确定的信号通过一个电阻钳位在高电平,此电阻还起到限流的作用。同理,下拉电阻是把不确定的信号钳位在低电平。上拉电阻是指器件的输入电流,而下拉指的是输出电流。

那么在什么时候使用上、下拉电阻呢?

1、当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,以提高输出的搞电平值。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在CMOS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限,增强抗干扰能力。

6、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

另外,上拉电阻阻值的选择原则包括:

1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理

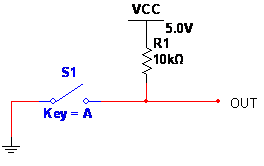

关于上拉电阻,看图。

作为输入接VCC等于1,接GND=0。

如果按键短路(按下)电阻为零,按键按下,Out=0,当按键断开,Out=?显然当Out悬空输出VCC,这可以用仪表测量。这个VCC就是靠R1“上拉”产生的,顾名思义,R1就是上拉电阻。上拉电阻的大小,取决于输出接负载的需要,通常逻辑电路对高电平输出阻抗很大,要求输出电流很小,在上拉电阻上压降可以忽略,当然上拉电阻不能太大,否则就不能忽略了。

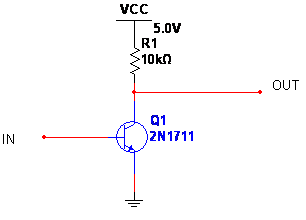

实际电路还有这种结构

这里的R1也是上拉电阻。

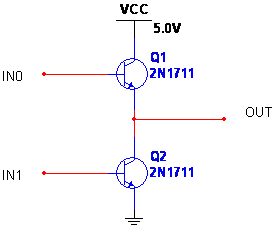

单片机P0口输出结构一部分电路类似下图,实际可能用的是场效应管。

当Q1,Q2分别导通,可以对外输出0和1,当Q1,Q2都不导通时?要想输出1,咋办?外接上拉电阻!

为什么要使用拉电阻:

一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

关于下拉电阻,用得少,道理和上面一样,只不过通过电阻“下拉”到GND。

这里不再详细说明

数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平,C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平。

上拉电阻是用来解决总线驱动能力不足时提供电流的。一般说法是拉电流,下拉电阻是用来吸收电流的,也就是灌电流。

1196661789

1196661789